## Highly Robust Single-Wall Carbon Nanotube-Molecule Junction Device Fabrication Process

Y. Shan<sup>1,4</sup>, S. Jeon<sup>2,4</sup>, C. Nuckolls<sup>2,4</sup>, S. J. Wind<sup>3,4</sup>, and J. Hone<sup>1,4</sup>

<sup>1</sup>Department of Mechanical Engineering, <sup>2</sup>Department of Chemistry, <sup>3</sup>Department of Applied Physics and Applied Mathematics, <sup>4</sup>Center for Electron Transport in Molecular Nanostructures Columbia University, New York, NY

The exceptional electrical properties of single-wall carbon nanotubes (SWNTs) make them prime candidates for the active element (i.e., channel) of future generation transistors. These properties also make them an excellent choice for source and drain electrodes in single-molecule devices. In addition to their electrical properties, SWNTs are composed of pure carbon, making them more conducive to the formation of stable chemical bonds with organic molecules, which is a problem with traditional gold electrodes. Furthermore, their small size reduces the phase space for bonding, make the molecular connection process easier. Such a SWNT-molecule device requires the formation of a nanoscale gap into which a single molecule can be inserted, which has proven to be quite challenging. Early SWNT-molecule device fabrication processes, which relied upon direct-write electron beam lithography, suffered from extremely low yield and poor repeatability. The process was also quite time-consuming.

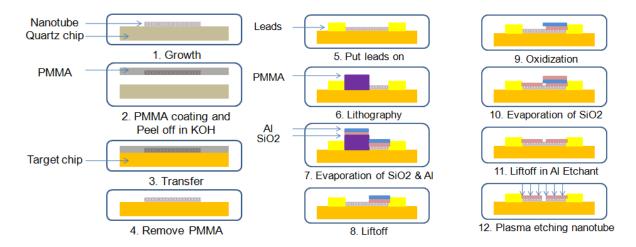

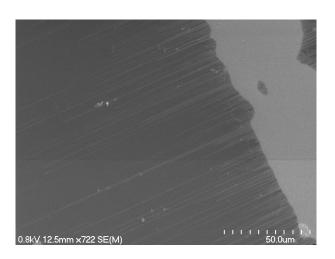

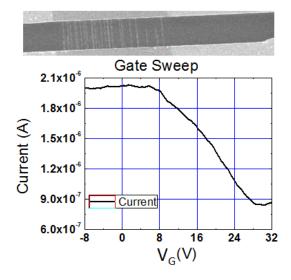

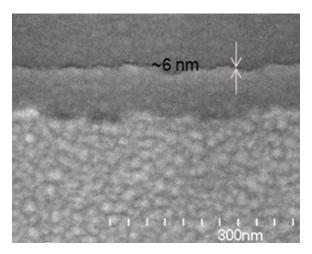

In this work, we report progress in achieving large-scale robust fabrication of SWNT-molecule junction devices. In our scheme, shown schematically in Fig. 1, an array ( $\sim$ 100's) of SWNT-molecule junction devices can be fabricated at the same time. Arrays of SWNTs are first grown on an s-cut quartz substrate, using a thin evaporated Co film. By carefully controlling the temperature, feedstock flow rate and thickness of the Co film, a dense array of well-aligned,  $\sim$  200  $\mu$ m long SWNTs can be grown at a desired location. The nanotubes are then transferred to a device chip using a process developed by Jiao et al., in which PMMA is used as a transfer medium. Figure 2 shows an array of SWNTs transferred from quartz to a Si<sub>3</sub>N<sub>4</sub> substrate. The SWNTs are subsequently wired with metal leads. Transfer characteristics of a parallel array of 19 SWNTS are shown in Fig. 3. A nanoscale gap is then created in the middle of the SWNTs by a self-aligned process. in Fig. 3. A nanoscale gap is determined by the self-limiting lateral oxidation of an ultrathin Al layer that is deposited on top of the SWNTs. This process is quite robust, allowing the creation of hundreds of sub10 nm gaps (Fig. 4) with a high degree of uniformity. The metal serves as a hard mask for the reactive ion etching of the underlying SWNTS. After etching, the metal can be removed, and molecules can be introduced into the gaps.

We will present details of the fabrication process for achieving large-scale arrays of SWNT- molecule junction devices. This process overcomes many of the difficulties encountered with the previous direct-write approach, representing an important step toward providing statistically significant measurements on single-molecule devices.

X. Guo, J. P. Small, J. E. Klare, Y. Wang, M. S. Purewal, I. W. Tam, B. H. Hong, R. Caldwell, L. Huang, S. O'Brien, J. Yan, R. Breslow, S. J. Wind, J. Hone, P. Kim and C. Nuckolls, Science 311 (5759), 356-359 (2006).

<sup>2.</sup> L. Venkataraman, J. E. Klare, I. W. Tam, C. Nuckolls, M. S. Hybertsen and M. L. Steigerwald, Nano Letters 6 (3), 458-462 (2006).

<sup>3.</sup> C. Kocabas, M. A. Meitl, A. Gaur, M. Shim and J. A. Rogers, Nano Letters 4 (12), 2421-2426 (2004).

<sup>4.</sup> L. Jiao, X. Xian, Z. Wu, J. Zhang and Z. Liu, Nano Letters (in press).

<sup>5.</sup> J. Tang, E. P. De Poortere, J. E. Klare, C. Nuckolls and S. J. Wind, Microelectronic Engineering 83 (4-9), 1706-1709 (2006).

J. Y. Tang, Y. L. Wang, J. E. Klare, G. S. Tulevski, S. J. Wind and C. Nuckolls, Angewandte Chemie-International Edition 46

(21), 3892-3895 (2007).

Figure 1. schematic of the lithography process.

**Figure 2.** SWCNT array transferred from S-cut quartz chip on to Si3N4 chip.

**Figure 3.** SWCNT array devices gate sweep ( $V_{SD} = 0.05V$ , channel width is 10 um).

Figure 4. Nanometer size gap created by multiple layer process.