## Arrays of 25 ×25 nm<sup>2</sup> Cross-Point Resistive Switching Devices Fabricated with Nanoimprint Lithography

Qiangfei Xia\*

Department of Electrical and Computer Engineering, University of Massachusetts, Amherst, MA 01003

Transition metal oxide based resistive switching devices (memristors) are promising candidates for the next generation non-volatile random access memory (NV-RAM) [1, 2]. Due to its simplicity and scalability in structure, cross-point architecture has been widely used for these devices. Nanoimprint lithography (NIL) [3] has proved to be the cost-effective technique for fabricating working TiO<sub>2</sub>-based devices with junction area of  $50 \times 50 \text{ nm}^2$  [4].

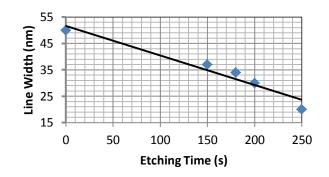

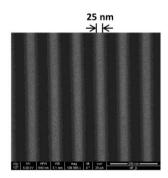

Here we present arrays of TiO<sub>2</sub>-based cross point resistive switching devices with junction area of 25 × 25 nm<sup>2</sup> using NIL. To fabricate the imprint mold, we started with a master mold (100 nm thick thermal SiO<sub>2</sub> on Si) that has arrays of 50 nm wide nanowires and microscale fanouts and contact pads patterned by electron beam lithography (EBL) and photolithography. Diluted HF (1:50) was then used to shrink the feature size and the lateral etching rate of SiO<sub>2</sub> is about 1.1 Å/s (Figure 1). With careful control of the etching time, and constant stirring of the solution (~1Hz magnetic spin bar), the line width of the SiO<sub>2</sub> mold was shrunk to 25 nm (Figure 2). The features were then duplicated to a quartz (QZ) substrate using NIL and reactive ion etching (RIE).

In device fabrication, we used NIL for both the bottom and top electrodes. First, double layer resists consisting of an underlayer that dissolves in acetone and a UV-curable top layer that cross-links upon the UV radiation were spin coated onto a SiO<sub>2</sub>/Si substrate. UV-NIL using the QZ mold was then carried out to pattern the device structures into the UV-curable layer. The residual cross-linked UV resist and the underlayer were etched by RIE using fluorine and oxygen based etching chemistry, respectively. After depositing 4 nm Ti and 12 nm Pt in an electron gun evaporator and a lift off process in acetone, a 29 nm thick TiO<sub>2</sub> film was sputter coated onto the substrate at a temperature of about 270°C in a direct current (DC) sputtering system. Lastly, the top electrode (16 nm thick Pt) was fabricated on the TiO<sub>2</sub> switching layer using NIL, RIE, metal deposition and liftoff. Fig. 3 shows scanning electron microscope (SEM) images of the device arrays with junction area about 25 ×25 nm<sup>2</sup>.

The current method provides a simple approach to make cross point devices with small junction areas. The electrical characterization of the small-area devices will also be reported.

<sup>[1].</sup> Chua, L. O. IEEE Trans. Circuit Theory 18, 507-519 (1971).

<sup>[2].</sup> Strukov, D. B.; Snider, G. S.; Stewart, D. R.; Williams, R. S. Nature 453, 80-83 (2008).

<sup>[3].</sup> Chou, S. Y.; Krauss, P. R.; Renstrom, P. J. Science 272, 85-87 (1996).

<sup>[4].</sup> Yang, J. J et al. Nature Nanotech. 3, 429 - 433 (2008).

<sup>&</sup>lt;sup>\*</sup> Email: qxia@ecs.umass.edu

**Figure 1.** The line width of an originally 50 nm wide SiO<sub>2</sub> nanowire mold as a function of etching time in 1:50 diluted HF solution. The solution was constantly stirred using a magnetic spin bar at 1 Hz.

| 25 nm               |                                                       |

|---------------------|-------------------------------------------------------|

|                     | ****                                                  |

|                     |                                                       |

|                     |                                                       |

|                     |                                                       |

|                     | 16 nm Pt                                              |

|                     | 29 nm TiO2<br>4 nm Ti/12nm Pt                         |

| X 105,000 S.0KV SET | Substrate<br>One JEOL 1/13/2011<br>DEM NO See 3:54:49 |

**Figure 3.** An array of cross-point devices with 25 ×25 nm<sup>2</sup> junction areas. The cross sectional device geometry is schematically shown in the inset (not to scale).