## Memory characteristics of MOS capacitors with Ptnanoparticles-embedded gate layers

<u>Sungsu Kim<sup>1</sup></u>, Kyoungah Cho<sup>1</sup>, Sangsig Kim<sup>\*1,2</sup>

<sup>1</sup>Department of Electrical Engineering, Korea University, Seoul 136-713, Korea <sup>2</sup>Department of Nano Semiconductor Engineering, Korea University, Seoul 136-713, Korea \*sangsig@korea.ac.kr

Recently, room-temperature processable fabrication for nonvolatile memory devices has attracted considerable attention since plastic based devices considered as one of promising next-generation devices are vulnerable to heat [1~3]. Especially, nano-floating gate memory (NFGM) structures containing nanoparticles embedded in gate layers have been fabricated using nanoparticle synthesized in solution at room temperature[4,5]. However, solution processable fabrication meets a hindrance to solve for reproducibility. Therefore, in this study, we propose new room-temperature processable fabrication for NFGM by utilizing Pt nanoparticles (NPs) sputtered in system with a cooling unit.

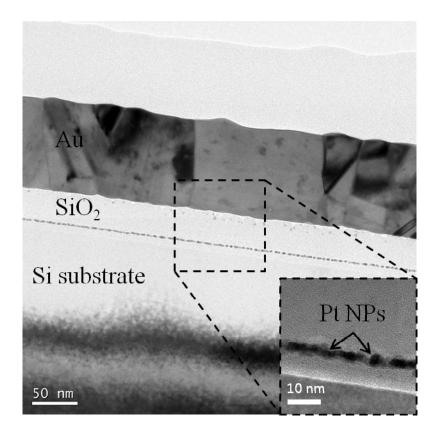

Pt NPs were formed on SiO<sub>2</sub> layers with a thickness of 6.3 nm on top of silicon (p-type, (100)) wafers by DC magnetron sputtering method and the SiO<sub>2</sub> layers were used as the tunneling oxides. Control oxide layers of SiO<sub>2</sub> with a thickness of 35 nm were then deposited by RF magnetron sputtering. Subsequently, top electrodes of Au were deposited on the control oxide layers by thermal evaporation. The structure and electrical characteristics of our devices were examined with transmission electron microscope (TEM) and a semiconductor parameter analyzer, respectively.

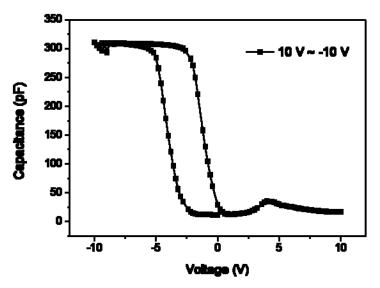

Figure 1 shows cross-sectional TEM images of MOS capacitors with Pt-NPsembedded gate layers. The sputtered Pt NPs with an average size of 4 nm diameter are formed isolatedly from each other between the tunneling and the control oxide layers. The capacitance versus voltage (C-V) curves obtained at 1 MHz are exhibited in Fig. 2. The flat-band voltage shift of 2.8 V is observed in a counter clock wise direction when voltage is swept from +10 to -10 V, indicating the storage of injected holes on Pt NPs.

References

- [1] Tsuyoshi Sekitani, et al. Science 326 (5959), 1516-1519. (2009).

- [2] Ricky J. Tseng et al. Nano Letters 5 (6), 1077-1080 (2005).

- [3] K. N. Narayanan Unni, Remi de Bettignies, Sylvie Dabos-Seignon, and Jean-Michel Nunzi, Appl. Phys. Lett **85**, 1823(2004).

- [4] Dong-young Jeong, Kihyun Keem, Byoungjun Park, Kyoungah Cho, and Sangsig Kim, IEEE Trans. Nanotechnol. **8**, 5 (2009)

- [5] Leong, Wei Lin et al. Adv. Mater. 20, 12 (2008).

Figure 1: Cross-sectional TEM Images of a MOS capacitor with a Pt-NPsembedded gate layer

Figure 2: High -frequency C-V curves of a MOS capacitor with a Pt-NPs-embedded gate layer