## Sub-10 nm silicon pattern transfer using PS-PDMS block-copolymer

D. L. Olynick, \*Z. Liu, \*\*, X, Gu, \* S. Sassolini\*, B. Muddiman\*, J. J. Hwu, b

\*The Molecular Foundry, Lawrence Berkeley National Laboratory, MS 67R2206 Berkeley, CA 94720; <u>dlolynick@lbl.gov</u> <sup>+</sup>Oxford Instruments, Concord, Massachusetts, 01742 <sup>b</sup>Seagate Technology, Fremont, California 94538 <sup>#</sup>Dept. Polymer Science and Engineering, University of Massachusetts, Amherst

Patterning using block copolymer directed self-assembly is a powerful technique for high density nanomanufacturing, for example in semiconductor patterning or bit patterned storage media. To capitalize on advances in BCP lithography, plasma pattern transfer must advance in parallel. Here we show pattern transfer of 10-15 nm features into silicon using masks derived from PS-PDMS block copolymer (BCP) lithography. We used cryogenic temperature  $Sf_6-O_2$  to plasma etch silicon using. Masks were patterned using both spherical and cylinder forming PS-b-PDMS towards wire and fin type patters. After phase segregation, the PS matrix was etched away to leave the oxidized PDMS minority phase. Subsequently, the pattern was used in the silicon etching chemistry or transferred to a hard mask, for instance, via the plasma etching of chromium. A selective atomic layer deposition process was also investigated.

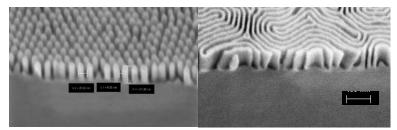

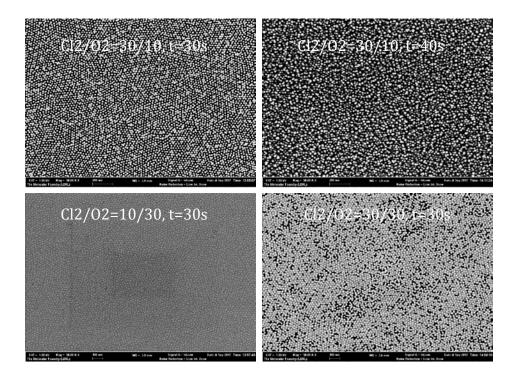

The best pattern transfer was achieved using the chromium hard mask (Figure 1, 10 nm thick for the dots and 5 nm for the lines). The chromium etch recipe development is shown in Figure 2. The film was etched in an ICP with a low forward bias to maximize selectivity to the PDMS mask. A ratio  $30/10 \text{ Cl}_2/\text{O}_2$  gave the best results. However, etching much more than 30 seconds produced an undercut of the PDMS allowing the PDMS to migrate from its original position destroying the patter (40 second etching). In addition, the etch rate is temperature dependent. Without active temperature control, the etch rate accelerated and undercut the chromium mask.

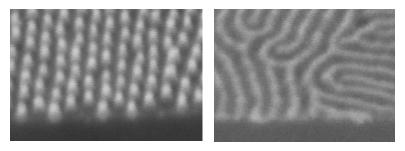

With regard to PDMS line patterns, the 10 nm chromium layer had to be thinned; the etch rate for the chromium lines was significantly slower than the dot pattern etch rate and the PDMS to Cr selectivity was insufficient to etch 10 nm thick lines. Figure 3 shows cross-sections of etched dot and line patterns in chromium. Size control with chromium etching and alternative mask patterning techniques will also be shown. In addition, the importance of the ion angular distribution will be discussed in the context of all three masking techniques: direct-etch with PDMS, chromium hard mask, and selective ALD.

Figure 1: Silicon posts and fins plasma etched at cryogenic temperature in  $SF_6/O_2$  using chromium hard mask. Scale bar on right is 100 nm. Images are taken at a 45 degree tilt.

Figure 2: Comparison of different  $Cl_2$  to  $O_2$  flow ratios and etching times for chromium etching step. The best ratio was 30  $Cl_2$  to 10  $O_2$  with a time of ~30 seconds for these patterns. With longer etching times, the PDMS can migrate off the chromium dots and/or be etched away. Too much oxygen slows down the chromium etching rate such that it does not etch or etches too slowly (bottom left and right).

Figure 3: Left, 10 nm thick chromium etched using PDMS sphere mask. Right, 5 nm thick chromium etched using PDMS cylinder mask.