## Design Strategy for Layout of Sub-Resolution Directed Self-Assembly Assist Features (SDRAFs)

Maryann C. Tung<sup>1</sup>, Jan Doise<sup>2,3</sup>, Ioannis Karageorgos<sup>2,3</sup>, Julien Ryckaert<sup>2</sup>, H.-S. Philip Wong<sup>1</sup>

<sup>1</sup>Dept. of Electrical Engineering and Stanford SystemX Alliance, Stanford University, Stanford, CA 94305, USA <sup>2</sup>imec, Kapeldreef 75, B-3001 Leuven, Belgium <sup>3</sup>Dept. of Electrical Engineering (ESAT), Katholieke Universiteit Leuven, B-3001, Leuven, Belgium tungmc@stanford.edu

In the pursuit of alternatives to optical lithography, block copolymer directed self-assembly (DSA) has emerged as a low-cost, high-throughput option. DSA uses small topographical templates to contain the block copolymer and create small clusters of holes useful for patterning vias [1]. However, issues of defectivity have hampered DSA's viability for large-scale patterning. Recent studies have shown polymer fill level to be a crucial factor in defectivity, as template overfill can result in malformed DSA structures [2]. The inherent density variations in via layouts, though, make regions of overfilled templates nearly inevitable, as templates in less dense regions will contain more polymer.

For this reason, we develop a method to integrate sub-DSA resolution assist features (SDRAFs) into DSA template layouts. The SDRAFs divert excess polymer from the overfilled main templates but are themselves too small to form transferrable DSA patterns [2]. Thus, we can populate low-density regions with SDRAFs to make a layout more uniformly dense. To do this, we with a set of lithography-based design rules dictating the minimum pitch and resist thickness between features (95 nm and 45 nm for 193i, respectively). The SDRAF CD is also chosen to be as large as possible without forming a transferrable DSA pattern, setting it at 40 nm for an  $L_0 = 40$  nm polymer and a PS wetting flow.

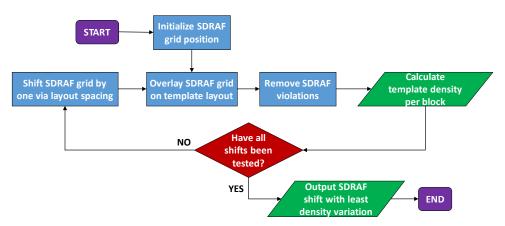

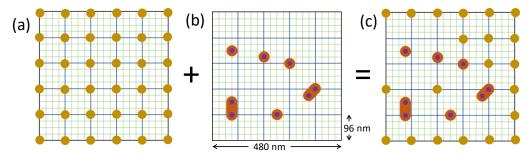

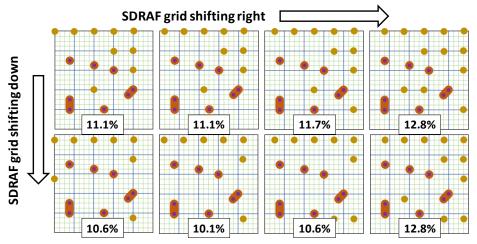

With these rules, we can assign the SDRAF according to the flow in Fig. 1. We demonstrate the process on a 2.5 x 2.5 µm section from V23 (the via layer connecting metals 2 and 3) of a routed N7 Cortex-M0 processor scaled to a 24 nm via layout grid. As shown in Fig. 2, we first overlay the template layout with a grid of SDRAFs spaced at 96 nm, allowing the SDRAFs to align with the via grid. We then remove the SDRAFs that violate the minimum resist or pitch rules and assess the density result. This is done by dividing the layout into blocks and calculating the percentage of area occupied by the main and assist templates in the blocks, using prior experimental data for template area [3]. The size of the blocks is set to the length over which the polymer reflows during the thermal anneal [4], assumed here to be about 500 nm. Finally, the SDRAF grid is shifted vertically and horizontally in increments of the via grid (24 nm) to achieve different density results, as each shift causes different SDRAFs to be in violation (see Fig. 3). We can then choose the shift that minimizes the density variation across the blocks as the final layout. In our test case, we found that the density range of the blocks changed from 2.8-8.6% to 10.9-12.9% post-SDRAF assignment. Here, the polymer film thickness can be adjusted to accommodate the higher overall density and the narrowed density range shows promise to reduce template overfill. Future work will incorporate methods of improving the layout's PV band to create an SDRAF design strategy that is more DSA- and lithography-friendly.

[1] H. Yi *et al.*, Adv. Mater **24**, 23 (2012). [2] H. Yi *et al.*, Proc. SPIE **9423**, 1F (2015). [3] J. Doise *et al.*, J. Vac. Sci. Technol. B **33**, 6 (2015). [4] H. Yi *et al.*, Proc. SPIE **9323**, 2A (2015).

Figure 1: Flowchart for the SDRAF placement scheme. The grid of SDRAFs is shifted to each position and the density of templates in each block is calculated. When all the SDRAF positions have been tested, the one with the lowest density variation is returned.

Figure 2: Example of SDRAF assignment process. In overlaying the grid of SDRAFs (a) onto the template layout (b), several SDRAFs must be removed to in order to adhere to minimum pitch and resist requirements. The resulting template layout with compliant SDRAFs is given in (c), where the yellow circles are the SDRAFs and the orange shapes the main templates enclosing the purple vias.

Figure 3: Partial example of the SDRAF shifting process. For this via and SDRAF grid pairing, the SDRAF grid can shift vertically and horizontally four times before repeating, totaling sixteen shifts. As they, different SDRAFs are removed and the area usage changes (the density of the block is given above for each shift).