## Process Simulation of Si Dot Fabrication for SETs by Ion Beam Mixing and Phase Separation in Nanopillars

<u>T. Prüfer</u>, K.H. Heinig, W. Möller, G. Hlawacek, X. Xu, J. von Borany, S. Facsko, R. Hübner, D. Wolf, L. Bischoff Institute for Ion Beam Physics and Materials Research, Helmholtz-Zentrum Dresden-Rossendorf, 01328 Dresden, Germany t.pruefer@hzdr.de

The single electron transistor (SET) is considered a promising candidate to continue the revolution of information technology due to its very low energy consumption (~100 times less then common FET). The big challenge is the manufacturability of SETs working at room temperature (RT). This requires the fabrication of much smaller structures (<5nm) than present-day and even future (multi-E-beam or EUV) lithography can provide.

Here we propose an ion-beam-assisted, CMOS compatible fabrication process of SETs. To realize the controlled tunneling of single electrons we propose a nanopillar of a Si/SiO<sub>2</sub>/Si stack with a single Si quantum dot embedded in SiO<sub>2</sub> and connected by tunnel junctions to Si electrodes, which makes the drain and source. For RT operation the quantum dot has to be smaller than 5nm and requires tunnel distances lower than 2nm. The size of this pillar needs to be in the range of 10-20nm.

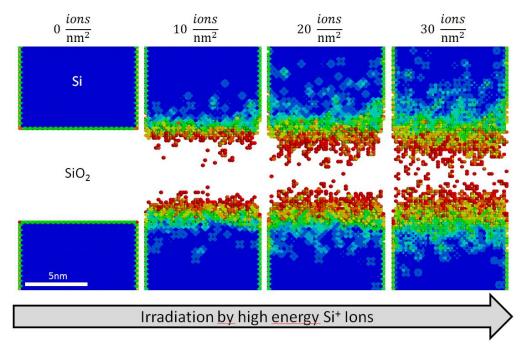

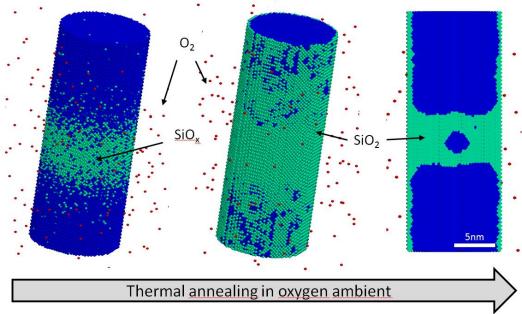

In this presentation we show the simulation of a CMOS compatible process to fabricate this quantum dot by using ion beam mixing and self-assembly. Earlier projects<sup>1</sup> proved already the reliability of dot formations using ion beam mixing technologies. Starting with a layerstack of Si/SiO<sub>2</sub>/Si, the ion beam irradiation by high energy Si<sup>+</sup> ions causes mixing of the two Si/SiO<sub>2</sub> interfaces what transforms the SiO<sub>2</sub> layer into metastable SiO<sub>x</sub> (Figure 1). During subsequent heat treatment the mixed region of SiO<sub>x</sub> (<10nm<sup>2</sup>) separates into Si and SiO<sub>2</sub>, what leads to the formation of one single Si nanodot in the SiO<sub>2</sub> layer (Figure 2). The irradiation simulations are done by TRIDYN<sup>2</sup> and TRI3DYN<sup>3</sup> program codes and the annealing by a self-developed Kinetic Monte Carlo program. We will present, how this process can be controlled using the ion beam irradiation values, geometrical sizes and the heat treatment parameters, so that it is yielding suitable conditions for application in hybrid SET-CMOS devices operating at RT.

This part of the work is being funded by the European Union's Horizon 2020 research and innovation program under Grant Agreement No 688072 (Project IONS4SET).

<sup>&</sup>lt;sup>1</sup> L. Röntzsch, at al., phys. Stat. sol. (a) 202, 15, R170-R172 (2005)

<sup>&</sup>lt;sup>2</sup> W. Möller, W. Eckstein, Nucl. Instr. and Meth. in Phys. Res. B2 (1984) 814

<sup>&</sup>lt;sup>3</sup> W. Möller, Nucl. Instr. and Meth. in Phys. Res. B, vol. 322, 23-33 (2014)

Figure 1: A cut threw a Si nanopillar with a 7nm thin SiO<sub>2</sub> layer: The simulated mixing at the Si/SiO<sub>2</sub> interfaces with increasing 50keV Si<sup>+</sup> fluences is shown.

Figure 2: Simulation of the thermally activated phase separation in the ion beam mixed nanopillar: At appropriate  $Si^+$  fluences, pillar sizes and  $SiO_2$  layer thicknesses, a single Si quantum dot self-assembles. Self-assembly is supported by simultaneous oxidation forming the oxide for the gate-all-around nanopillar SET.