## Ruthenium Patterning via Reactive Ion Etching for EUV optics

Sharon Oh, Weilun Chao, Farhad Salmassi, Patrick Naulleau Center for X-Ray Optics, Lawrence Berkeley National Lab, Berkeley, CA 94720 sharonoh@lbl.gov

Extreme ultraviolet (EUV) has received significant attention in the past decades due to the development of next generation semiconductor lithography. Even though high reflectivity multilayer mirrors are the choice of optics in EUV lithography, diffractive optics such as gratings and Fresnel zoneplates are favorable due to their compactness and lower cost, and are thus used for EUV mask research<sup>1</sup>. Contrary to conventional belief, EUV diffractive optics can possess diffraction efficiencies as high as 30%. The key is to fabricate the optics with materials of strong phase shift and low absorption at the EUV wavelength. For example, the theoretical transmission grating efficiency is 27% with 55nm thick Ru<sup>2</sup>.

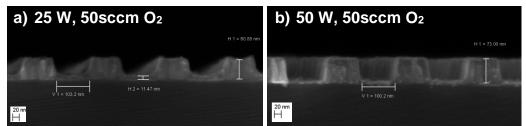

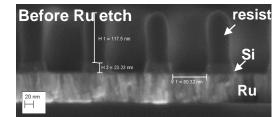

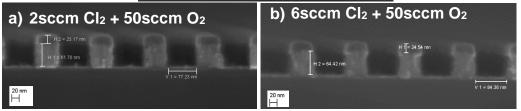

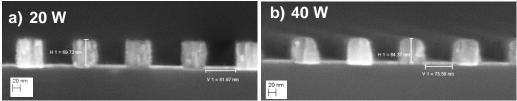

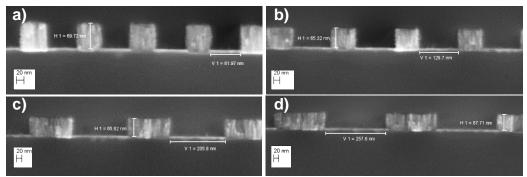

We have developed a Ru patterning process using electron beam lithography and repeatable reactive ion etching pattern transfer. Dense line patterns below 80 nm half-period were exposed to ZEP 520A and subsequently transferred into a silicon hard mask and a ruthenium layer. Silicon was chosen as our etch process had high selectivity between Ru to Si for pattern transfer (> 70:1), as well as hard mask removal. For silicon mask etching, anisotropic cryogenic etching with SF<sub>6</sub> and O<sub>2</sub> was used<sup>3</sup>. For pattern transfer, Ru can be chemically etched via O<sub>2</sub>-containing RIE as a volatile etch product,  $RuO_4$ , is produced<sup>4</sup>. In our etches, inductively coupled plasma (ICP) was used in conjunction with RIE to improve anisotropy. Higher RF power from 25 W (Figure 1a) to 50 W (Figure 1b) resulted in a more desirable vertical sidewall slope without significant mask loss. While Ru can be etched by pure  $O_2$  RIE, it is known in the literature that the etch rate is dramatically increased by the inclusion of  $Cl_2$ <sup>5</sup>. We found that adding  $Cl_2$  not only increased the etch rate but also changed sidewall slopes from positive to negative, at the expense of sidewall roughness (Figure 2a and b). It was found that adding just a small amount of Cl<sub>2</sub> (2 sccm) to 50 sccm of O<sub>2</sub> is sufficient to yield vertical sidewalls after etching Ru for 4 min, for an etch depth of 70 nm. Finally, SF<sub>6</sub> and CF<sub>4</sub> RIE was used to remove the Si mask, with low RF power to prevent the rounded top profiles caused by excessive mask erosion at the edges (Figure 3). Using our optimized etching process, we successfully fabricated Ru lines of varying sizes with a vertical profile in the same etch (Figure 4). In the presentation, we will discuss optimization of the etch process and the efficiency performance of Ru gratings fabricated using this process.

<sup>&</sup>lt;sup>1</sup> M. P. Benk et al, J. Micro/Nanolith. MEMS MOEMS, 14, 1 (2015).

<sup>&</sup>lt;sup>2</sup> "CXRO X-Ray Interactions With Matter", http://henke.lbl.gov/optical\_constants/

<sup>&</sup>lt;sup>3</sup> Z. Liu, Y. Wu, B. Harteneck, and D. Olynick, Nanotechnology, 24, 1 (2012)

<sup>&</sup>lt;sup>4</sup> C. C. Hsu, J. W. Coburn, and D. B. Graves, J. Vac. Sci. Technol A, 24, 1 (2006)

<sup>&</sup>lt;sup>5</sup> H. W. Kim and C.-J. Kang, Microelectron. Eng., **69**, 1 (2003)

*Figure 1:* Cross-sectional SEM images of Ru lines etched at different RF powers, showing a more desirable vertical sidewall slope with increased RF power. Cr instead of Si was used as a mask.

*Figure 2:* Cross-sectional SEM images showing smoother etched sidewalls for Ru lines with less added Cl<sub>2</sub>. The resist was entirely removed, but the Si hard mask above Ru was mostly intact.

*Figure 3:* Cross-sectional SEM images taken after RIE removal of Si mask with RF at (a) 20 W; (b) 40 W, showing rounded top profiles caused by mask erosion.

*Figure 4:* Cross-sectional SEM micrographs of etched Ru lines of varying widths on the same chip.