## Improving Current On/Off Ratio of Oxygen-Doped WSe<sub>2</sub> transistors by Selective Scanning Probe Lithography

S. Chen, Y. Zhang, W.P. King, A.M. van der Zande, R. Bashir Department of Mechanical Science and Engineering, University of Illinois Urbana-Champaign, Urbana IL 61801

<u>rbashir@illinois.edu</u>; arendv@illinois.edu

WSe<sub>2</sub> is a prototypical p-type 2D semiconductor for nano-electronics, but its transistor performance remains contact-limited. Fermi level pinning at the metal-semiconductor interface causes large Schottky barriers.<sup>1</sup> One potential solution is to degenerately dope WSe<sub>2</sub> in the contact region to reduce the Schottky barrier width to facilitate tunneling. Oxidizing the topmost layer of WSe<sub>2</sub> results in stable hole doping without damaging underlying WSe<sub>2</sub> layers, achieving one of the lowest contact resistances in WSe<sub>2</sub>.<sup>2</sup> However, degenerately doped WSe<sub>2</sub> channel cannot be turned off for use as transistors. Here we use a scanning probe to selectively remove WO<sub>x</sub> on WSe<sub>2</sub>, which significantly improves the current on/off ratio of oxygen-doped WSe<sub>2</sub> transistors while preserving their high on-current.

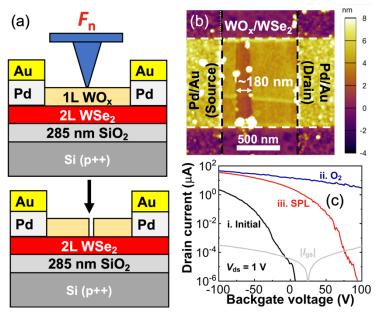

Figure 1a shows the schematic of device fabrication. A gentle remote O<sub>2</sub> plasma process oxidizes the topmost layer of Pd/Au contacted tri-layer WSe<sub>2</sub> field-effect transistor (FET) on SiO<sub>2</sub>/Si. Next, a diamond-coated atomic force microscope (AFM) tip<sup>3</sup> selectively scratches off WO<sub>x</sub> on WSe<sub>2</sub> in contact mode.

Figures 1b and 1c show the AFM image of an example FET and its transfer curves as measured at each stage of fabrication. The FET had an on-current of 2.2  $\mu$ A/ $\mu$ m and an on/off ratio of  $4\times10^4$  as fabricated, an on-current of 46  $\mu$ A/ $\mu$ m and an on/off ratio of 16 after remote  $O_2$  plasma, and an on-current of 36  $\mu$ A/ $\mu$ m and an on/off ratio of  $3\times10^5$  after SPL. Selective removal of WO<sub>x</sub> improved the current on/off ratio by  $2\times10^4$  while the on-current decreased slightly by 22%.

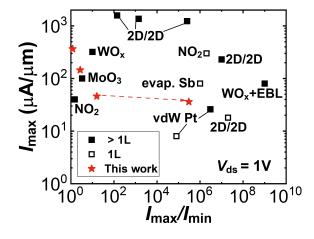

Figure 2 benchmarks the performance of oxidized few-layer WSe<sub>2</sub> FETs in this work with the state-of-the-art p-type transition metal dichalcogenide transistors.

This works shows the potential of selectively oxidized few-layer WSe<sub>2</sub> to fabricate high-performance short channel transistors that meet the demand for next-generation electronics. The same selective SPL strategy can also be applied to other molecular dopants in fabricating short channel 2D transistors.

<sup>&</sup>lt;sup>1</sup> Y. Xu, C. Cheng, S. Du, J. Yang, B. Yu, J. Luo, W. Yin, E. Li, S. Dong, P. Ye, and X. Duan, ACS Nano **10**, (2016).

<sup>&</sup>lt;sup>2</sup> A. Borah, A. Nipane, M.S. Choi, J. Hone, and J.T. Teherani, ACS Appl. Electron. Mater. **3**, 2941 (2021).

<sup>&</sup>lt;sup>3</sup> P.C. Fletcher, J.R. Felts, Z. Dai, T.D. Jacobs, H. Zeng, W. Lee, P.E. Sheehan, J.A. Carlisle, R.W. Carpick, and W.P. King, ACS Nano 4, 3338 (2010).

Figure 1: (a) Schematic of the use of an AFM tip to selectively remove monolayer (1L)  $WO_x$  on a bilayer (2L)  $WSe_2$  FET. (b) AFM topography of an example FET shown in (a). (c) Transfer curves of the example FET as-fabricated (i. Initial), after remote  $O_2$  plasma (ii.  $O_2$ ), and after scanning probe lithography (iii. SPL). Gate leakage current  $|I_{gs}|$  in stage iii is plotted in gray.

Figure 2: Benchmark plot of the state-of-the-art p-type transition metal dichalcogenide transistors with oxidized few-layer WSe<sub>2</sub> FETs in this work.