## Vertical Trench Etching by Repetitive Dry and Wet Anisotropic Etching and 3D Self-aligned Sidewall Nano-patterning

<u>Y. Pordeli</u>, C. Steenge, J.W. Berenschot, R.J.E. Hueting, N.R. Tas MESA+ Institute, University of Twente, The Netherlands y.pordeli@utwente.nl, n.r.tas@utwente.nl

A. Migliorini and S.S.P Parkin Max-Planck Institute of Microstructure Physics, Halle (Saale), Germany

3D stacking of nano-devices is an efficient way to increase areal density where further downscaling of lateral device dimension runs against fundamental, practical, or economical limits. A good example of this approach is in V-NAND or 3D-NAND memory systems<sup>1</sup>, where stacking is achieved mainly by employing plasma processing. Plasma etching features was previously used as a template for self-aligned mask formation using so-called edge and corner lithography, after which sidewall features can be formed by crystallographic etching techniques<sup>2,3</sup>. To explore smaller length scales in self-aligned sidewall patterning, the feature size and shape must be better defined, which has been investigated in this work by incorporating crystallographic wet etching in the trench formation process. The repetitive combination of dry and wet etching has been reported before for nanowire formation<sup>4</sup>, but not on the sub 200 nm scale or for sub 20 nm sidewall patterning as demonstrated in this work.

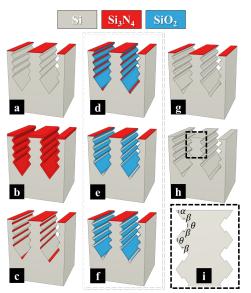

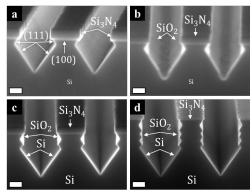

Nanometer-sized line patterns are formed wafer-scale on (100) Si substrates by displacement Talbot lithography, and an iteration of dry and wet etching steps is used to create vertically stacked wedge type structures at the sidewalls of the trenches defined by (111) surfaces (Fig. 1 and 2). In this method, a thin SiO<sub>2</sub> hard mask of ~4 nm is sufficient for this process. The concave corners of the vertically stacked trenches are further processed in a self-aligned manner (Fig. 3). Corner lithography is applied to protect all concave corners followed by thermal oxidation to protect all {111} planes. The concave corners are made accessible for further processing by timed etching of the Si<sub>3</sub>N<sub>4</sub> layer. Local sidewall nano patterning is demonstrated by creating diamond-like cavities after etching through the opened concave corners in KOH etchant (Fig. 4). The thus created new sharp corners and edges form templates for the self-aligned device fabrication.

<sup>&</sup>lt;sup>1</sup> Shim et al., Trends and future challenges of 3D NAND flash memory, IEEE International Memory Workshop, Monterey, CA, USA, 2023.

<sup>&</sup>lt;sup>2</sup> Westerik et al., Sidewall patterning – a new wafer-scale method for accurate patterning of vertical silicon structures, J. Micromech. Microeng. 28, 015008 (2018).

<sup>&</sup>lt;sup>3</sup> Ni et al., Wafer-scale 3D shaping of high aspect ratio structures by multistep plasma etching and corner lithography. Microsyst Nanoeng 6, 25 (2020).

<sup>&</sup>lt;sup>4</sup> He et al., Novel fabrication for vertically stacked inverted triangular and diamond-shaped silicon nanowires on (100) single crystal silicon wafer, J. Micromech. Microeng. 30, 015003 (2020).

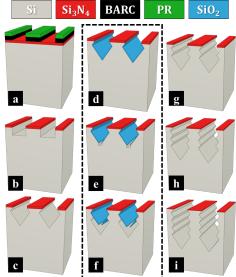

*Figure 1:* Schematic process flow of vertically stacked 3D nanostructures in (100) silicon. PR/BARC line patterning a) is followed by mixed mode RIE, resist strip b) and timed anisotropic silicon etching in KOH c). Iteration steps (indicated by a dashed box) consist of thermal oxidation d), directional RIE etching of SiO<sub>2</sub> e), and KOH etching f). SiO<sub>2</sub> hard mask stripping in HF g). Vertically stacked nanostructures after 2nd h) and 3rd i) iteration process respectively.

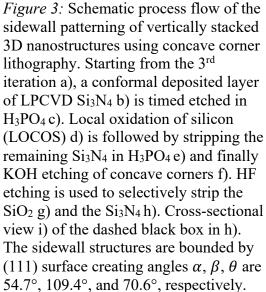

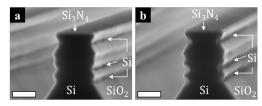

*Figure 2:* SEM images of fabricated vertically stacked 3D nanostructures after (a - c) single iteration, and after (d) three iterations. The scale bars are 100 nm.

*Figure 4:* SEM images of side-wall patterned nanostructures after corner lithography and KOH etching of the concave corners (a) and prolonged etching (b) to make it accessible for further processing. The scale bars are 100 nm.